2. MIPI 使用指南¶

2.1. 概述¶

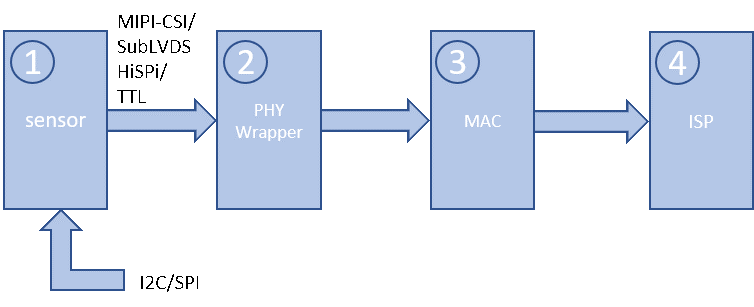

MIPI Rx可接收差分与DC(TTL)接口数据, 并将数据转换成pixel数据后传给下一级的ISP模块。 差分讯号支持SubLVDS(Sub Low-Voltage Differential Signal), MIPI-CSI与HiSPi(High-Speed Serial Pixel Interface)等视频输入。DC讯号支持Sensor RAW12, BT1120, BT656与BT601。

2.2. 重要概念¶

MIPI

移动行业处理器接口-Mobile Industry Processor Interface,MIPI特指物理层使用D-PHY传输规范并使用CSI-2为协议层的通信接口。

Lane

物理层用于连接发送端和接收端的一对高速差分线。一个Lane可传送时钟或数据。1C4D指一个时钟Lane及4个资料Lane。

LVDS

低压差分信号(Low Voltage differential Signaling),这里的LVDS泛指LVDS发展的sub-LVDS与HiSPi,通过同步码区分消隐区和有效数据。

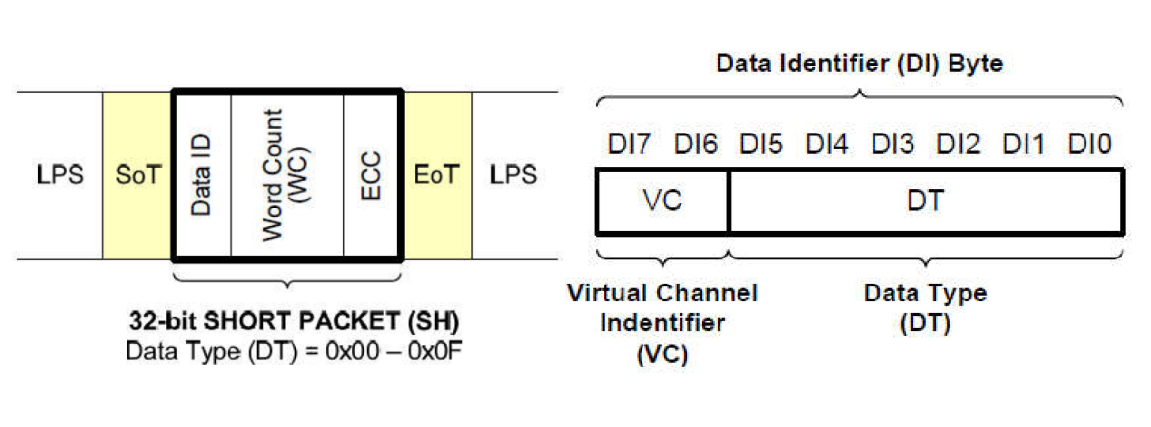

同步码

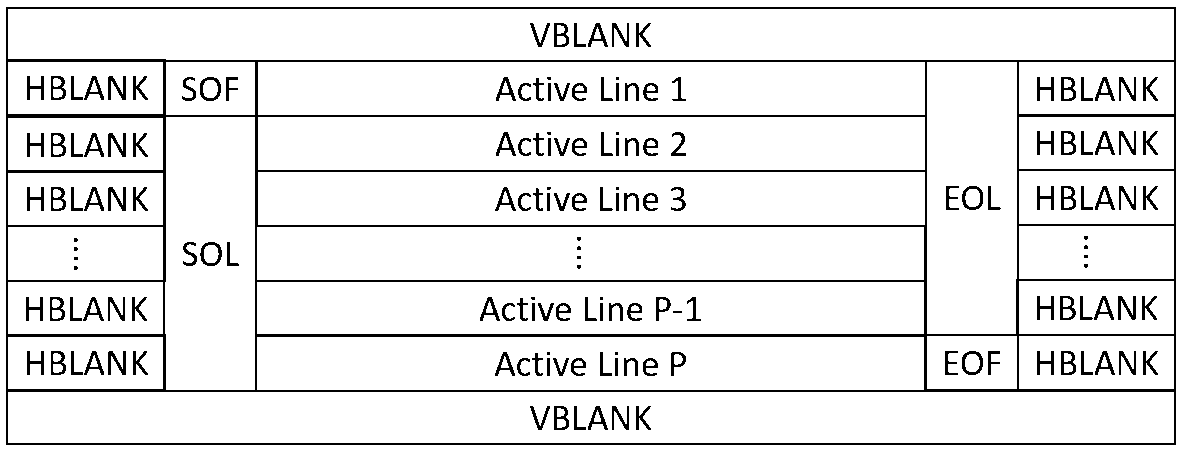

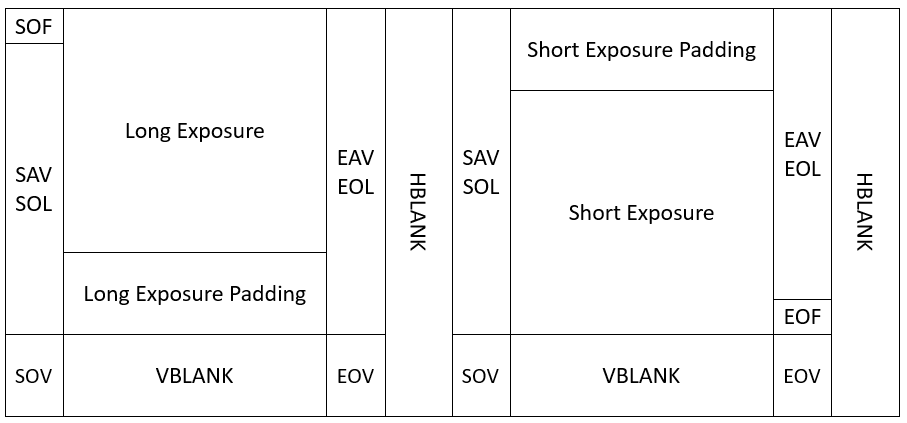

MIPI-CSI利用标准的短包(Short Packet)当做同步讯号。 LVDS讯号利用同包码(Sync Code)作为同步讯号。 LVDS有两种同步模式:

使用SOF/EOF表示一帧的开始与结束。

使用SOL/EOL表示行的开始与结束。

图 1‑1 SOF/EOF/SOL/EOL同步方式

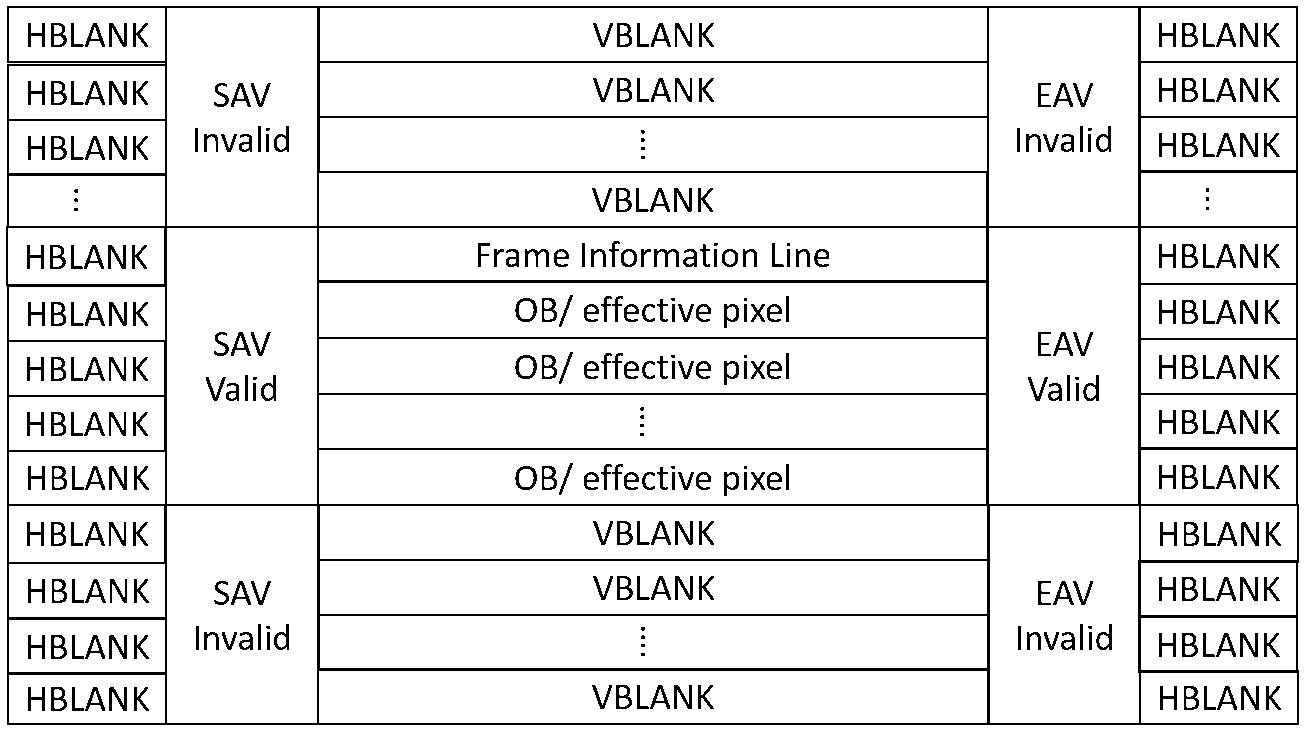

使用SAV invalid与EAV invalid表示VBLANK的开始与结束。 使用SAV valid与EAV valid表示有效数据(information line, H.OB与pixel data)的开始与结束。

图 1‑2 SAV/EAV同步方式

DOI

SONY的交错式WDR模式,全称为Digital Overlap。

2.3. 功能描述¶

MIPI RX支持一路最大4 lanes或两路最大2 lanes的MIPI-CSI,sub-LVDS 与HiSPi差分视频输入接口,接口支持lane互换与差分讯号的PN互换。注意若使用两路差分讯号输入,脚位MIPIRX#必须0到2同一组输入,3到5同一组输入。MIPI RX也支持sensor TTL,BT1120,BT656与BT601等平行输入接口,支持除了Clock以外的lane功能互换。 具体的Lane分布如下表:

表 1‑1 支持BT接口分布表. BGA封装支持VI0~VI2, QFN封装支持VI0.

VIO |

PAD NAME |

VI1 |

PAD NAME |

VI2 |

PAD NAME |

|---|---|---|---|---|---|

VIO_CLK |

MIPIRX4N |

VI1_CLK |

VIVO_CLK |

VI2_CLK |

VIDO_CLK |

VI0_D[0] |

MIPIRX4P |

VI1_D[0] |

VIVO_D0 |

VI2_D[0] |

VIVO_D0 |

VI0_D[1] |

MIPIRX3N |

VI1_D[1] |

VIVO_D1 |

VI2_D[1] |

VIVO_D1 |

VI0_D[2] |

MIPIRX3P |

VI1_D[2] |

VIVO_D2 |

VI2_D[2] |

VIVO_D2 |

VI0_D[3] |

MIPIRX2N |

VI1_D[3] |

VIVO_D3 |

VI2_D[3] |

VIVO_D3 |

VI0_D[4] |

MIPIRX2P |

VI1_D[4] |

VIVO_D4 |

VI2_D[4] |

VIVO_D4 |

VI0_D[5] |

MIPIRX1N |

VI1_D[5] |

VIVO_D5 |

VI2_D[5] |

VIVO_D5 |

VI0_D[6] |

MIPIRX1P |

VI1_D[6] |

VIVO_D6 |

VI2_D[6] |

VIVO_D6 |

VI0_D[7] |

MIPIRX0N |

VI1_D[7] |

VIVO_D7 |

VI2_D[7] |

VIVO_D7 |

VI0_D[8] |

MIPIRX0P |

VI1_D[8] |

VIVO_D8 |

||

VI0_D[9] |

MIPI_TXM0 |

VI1_D[9] |

VIVO_D9 |

||

VI0_D[10] |

MIPI_TXP0 |

VI1_D[10] |

VIVO_D10 |

||

VI0_D[11] |

MIPI_TXM1 |

VI1_D[11] |

MIPIRX5N |

||

VI0_D[12] |

MIPI_TXP1 |

VI1_D[12] |

MIPIRX5P |

||

VI0_D[13] |

MIPI_TXM2 |

VI1_D[13] |

MIPIRX4N |

||

VI0_D[14] |

MIPI_TXP2 |

VI1_D[14] |

MIPIRX4P |

||

VI1_D[15] |

MIPIRX3N |

||||

VI1_D[16] |

MIPIRX3P |

||||

VI1_D[17] |

MIPIRX2N |

||||

VI1_D[18] |

MIPIRX2P |

MIPI RX支持MIPI-CSI的解多任务 (CSI Demux),可接收不同channel ID的信道数据。

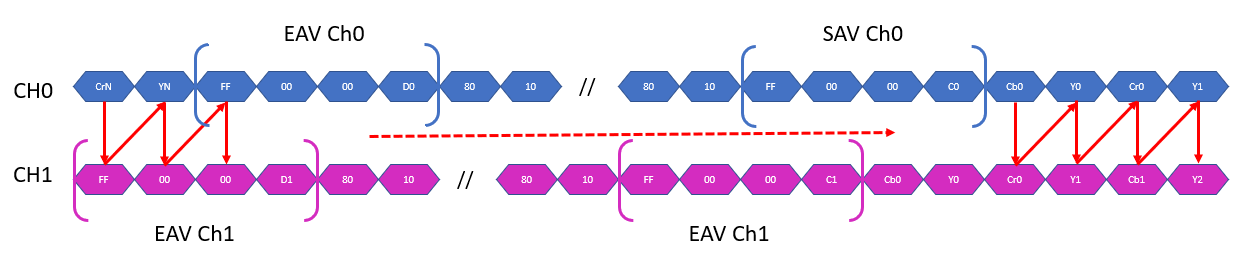

图 1-3 MIPI-CSI 的channel ID

MIPI RX支持BT接口的解多任务 (BT Demux),输入端将不同信道的数据以BT656字节交错的格式打包,MIPI RX可还原各通道再以对应的同步码解出有效数据。注意此模式只支持单沿取样(SDR)。

图 1‑4 BT demux模式支持的输入

2.4. API 参考¶

MIPI Rx提供对接sensor 时序的功能。 提供ioctl接口,可用的命令如下:

CVI_MIPI_SET_HS_MODE :CVI_MIPI_SET_HS_MODE: 设置MIPI的Lane分布模式。

CVI_MIPI_SET_DEV_ATTR :设置MIPI和并口设备属性。

CVI_MIPI_RESET_SENSOR :复位sensor。

CVI_MIPI_UNRESET_SENSOR :撤销复位sensor。

CVI_MIPI_RESET_MIPI :复位MIPI Rx。

CVI_MIPI_ENABLE_SENSOR_CLOCK :打开SENSOR的时钟。

CVI_MIPI_DISABLE_SENSOR_CLOCK :关闭SENSOR的时钟。

CVI_MIPI_SET_CROP_TOP :舍弃每帧中的首N条资料。

CVI_MIPI_SET_WDR_MANUAL :打开WDR手动模式。

CVI_MIPI_SET_LVDS_FP_VS :设定LVDS中VSYNC生成的时间点。

MIPI Tx提供对接显示屏、级联的功能。

其中单系统提供了ioctl接口,可通过传输以下相关命令进行相应的配置:

CVI_VIP_MIPI_TX_SET_DEV_CFG :设置MIPI Tx设备的属性。

CVI_VIP_MIPI_TX_GET_CMD :从MIPI Tx设备读取信息。

CVI_VIP_MIPI_TX_SET_CMD :设备发送命令给MIPI Tx设备。

CVI_VIP_MIPI_TX_ENABLE :启用MIPI Tx设备。

CVI_VIP_MIPI_TX_DISABLE :禁用MIPI Tx设备。

CVI_VIP_MIPI_TX_SET_HS_SETTLE :设定MIPI Tx在HS mode下的settle timing。

CVI_VIP_MIPI_TX_GET_HS_SETTLE :取得MIPI Tx在HS mode下的settle timing。

双系统提供了CVI_MSG_SendSync接口,可通过传输以下相关命令进行相应的配置:

MSG_CMD_MIPI_TX_SET_DEV_CFG :设置MIPI Tx设备的属性。

MSG_CMD_MIPI_TX_GET_CMD :从MIPI Tx设备读取信息。

MSG_CMD_MIPI_TX_SET_CMD :设备发送命令给MIPI Tx设备。

MSG_CMD_MIPI_TX_ENABLE :启用MIPI Tx设备。

MSG_CMD_MIPI_TX_DISABLE :禁用MIPI Tx设备。

MSG_CMD_MIPI_TX_SET_HS_SETTLE :设定MIPI Tx在HS mode下的settle timing。

MSG_CMD_MIPI_TX_GET_HS_SETTLE :取得MIPI Tx在HS mode下的settle timing。

2.4.1. CVI_MIPI_SET_HS_MODE¶

【描述】

相关功能被CVI_MIPI_SET_DEV_ATTR取代。

2.4.2. CVI_MIPI_SET_DEV_ATTR¶

【描述】

设置MIPI和并口设备属性。

【参数】

#define CVI_MIPI_SET_DEV_ATTR _IOW(CVI_MIPI_IOC_MAGIC, 0x01, struct combo_dev_attr_t)

【定义】

struct combo_dev_attr_t类型的指针。

【返回值】

返回值 |

描述 |

|---|---|

0 |

成功 |

-1 |

失败,并设置errno |

【处理器差异】

无

【需求】

头文件: cvi_vip_cif.h

【注意】

配置CVI_MIPI_SET_DEV_ATTR之前, 需要使用ISP接口打开MIPI_RX时钟. 详情请见ISP相关文件。

除了配置CVI_MIPI_SET_DEV_ATTR之前, 还需要配置以下接口。

复位MIPI: 接口为CVI_MIPI_RESET_MIPI。

打开Sensor的时钟: 接口为CVI_MIPI_ENABLE_SENSOR_CLOCK

复位Sensor: 接口为CVI_MIPI_RESET_SENSOR

撤销复位Sensor: 接口为CVI_MIPI_UNRESET_SENSOR

推荐的配置流程如下:

打开ISP时钟。

复位对接的Sensor。

复位MIPI Rx。

配置MIPI Rx设备属性。

打开Sensor所连接的时钟。

撤销复位对接的Sensor。

推荐的退出程序如下:

复位对接的Sensor。

关闭Sensor所连接的时钟。

复位MIPI Rx。

关闭ISP时钟。

操作Sensor复位信号线和时钟信号线会对所连接到该信号线的所有Sensor都产生效果。

【相关数据类型及接口】

CVI_MIPI_RESET_MIPI

CVI_MIPI_ENABLE_SENSOR_CLOCK关闭ISP时钟。

CVI_MIPI_DISABLE_SENSOR_CLOCK

CVI_MIPI_RESET_SENSOR

CVI_MIPI_UNRESET_SENSOR

2.4.3. CVI_MIPI_RESET_SENSOR¶

【描述】

复位sensor

【定义】

#define CVI_MIPI_RESET_SENSOR _IOW(CVI_MIPI_IOC_MAGIC, 0x05, unsigned int)

【参数】

unsigned int。 Sensor复位信号线编号。

【返回值】

返回值 |

描述 |

|---|---|

0 |

成功 |

-1 |

失败,并设置errno |

【处理器差异】

无

【需求】

头文件: cvi_vip_cif.h

【注意】

Sensor复位信号绑定在对应的dts。

mipi_rx: cif

{

compatible = "cvitek,cif";

reg = <0x0 0x0a0c2000 0x0 0x2000>, <0x0 0x0a0d0000 0x0 0x1000>,<0x0 0x0a0c4000 0x0 0x2000>;

reg-names = "csi_mac0", "csi_wrap0", "csi_mac1";

interrupts = <GIC_SPI 155 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 156 IRQ_TYPE_LEVEL_HIGH>;

interrupt-names = "csi0", "csi1";

snsr-reset = <&porta 2 GPIO_ACTIVE_LOW>, <&porta 2 GPIO_ACTIVE_LOW>;

resets = <&rst RST_CSIPHY0>, <&rst RST_CSIPHY1>,

<&rst RST_CSIPHY0RST_APB>, <&rst RST_CSIPHY1RST_APB>;

reset-names = "phy0", "phy1", "phy-apb0", "phy-apb1";

clocks = <&clk CV181X_CLK_CAM0>, <&clk CV181X_CLK_CAM1>, <&clk CV181X_CLK_SRC_VIP_SYS_2>;

clock-names = "clk_cam0", "clk_cam1", "clk_sys_2";

};

2.4.4. CVI_MIPI_UNRESET_SENSOR¶

【描述】

撤销复位sensor。

【定义】

#define CVI_MIPI_UNRESET_SENSOR _IOW(CVI_MIPI_IOC_MAGIC, 0x06, unsigned int)

【参数】

unsigned int。 Sensor复位信号线编号。

【返回值】

返回值 |

描述 |

|---|---|

0 |

成功 |

-1 |

失败,并设置errno |

【处理器差异】

无

【需求】

头文件: cvi_vip_cif.h

【注意】

Sensor复位信号绑定在对应的dts。

mipi_rx: cif

{

compatible = "cvitek,cif";

reg = <0x0 0x0a0c2000 0x0 0x2000>, <0x0 0x0a0d0000 0x0 0x1000>,

<0x0 0x0a0c4000 0x0 0x2000>;

reg-names = "csi_mac0", "csi_wrap0", "csi_mac1";

interrupts = <GIC_SPI 155 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 156 IRQ_TYPE_LEVEL_HIGH>;

interrupt-names = "csi0", "csi1";

snsr-reset = <&porta 2 GPIO_ACTIVE_LOW>, <&porta 2 GPIO_ACTIVE_LOW>;

resets = <&rst RST_CSIPHY0>, <&rst RST_CSIPHY1>,

<&rst RST_CSIPHY0RST_APB>, <&rst RST_CSIPHY1RST_APB>;

reset-names = "phy0", "phy1", "phy-apb0", "phy-apb1";

clocks = <&clk CV181X_CLK_CAM0>, <&clk CV181X_CLK_CAM1>, <&clk CV181X_CLK_SRC_VIP_SYS_2>;

clock-names = "clk_cam0", "clk_cam1", "clk_sys_2";

};

2.4.5. CVI_MIPI_RESET_MIPI¶

【描述】

复位MIPI_Rx。

【定义】

#define CVI_MIPI_RESET_MIPI _IOW(CVI_MIPI_IOC_MAGIC, 0x07, unsigned int)

【参数】

unsigned int。 MIPI_Rx设备号。

【返回值】

返回值 |

描述 |

|---|---|

0 |

成功 |

-1 |

失败,并设置errno |

【处理器差异】

无

【需求】

头文件: cvi_vip_cif.h

【注意】

无

2.4.6. CVI_MIPI_ENABLE_SENSOR_CLOCK¶

【描述】

打开Sensor的时钟。

【定义】

#define CVI_MIPI_ENABLE_SENSOR_CLOCK _IOW(CVI_MIPI_IOC_MAGIC, 0x10, unsigned int)

【参数】

unsigned int。 MIPI_Rx设备号。

【返回值】

返回值 |

描述 |

|---|---|

0 |

成功 |

-1 |

失败,并设置errno |

【处理器差异】

无

【需求】

头文件: cvi_vip_cif.h

【注意】

无

2.4.7. CVI_MIPI_DISABLE_SENSOR_CLOCK¶

【描述】

关闭Sensor的时钟。

【定义】

#define CVI_MIPI_DISABLE_SENSOR_CLOCK _IOW(CVI_MIPI_IOC_MAGIC, 0x11, unsigned int)

【参数】

unsigned int。 MIPI_Rx设备号。

【返回值】

返回值 |

描述 |

|---|---|

0 |

成功 |

-1 |

失败,并设置errno |

【处理器差异】

无

【需求】

头文件: cvi_vip_cif.h

【注意】

无

2.4.8. CVI_MIPI_SET_CROP_TOP¶

【描述】

舍弃每帧中的首N条资料

【定义】

#define CVI_MIPI_SET_WDR_MANUAL _IOW(CVI_MIPI_IOC_MAGIC, 0x21, struct crop_top_s)

【参数】

struct crop_top_s

【返回值】

返回值 |

描述 |

|---|---|

0 |

成功 |

-1 |

失败,并设置errno |

【处理器差异】

无

【需求】

头文件: cvi_vip_cif.h

【注意】

无

2.4.9. CVI_MIPI_SET_WDR_MANUAL¶

【描述】

打开WDR手动模式。

【定义】

#define CVI_MIPI_SET_WDR_MANUAL _IOW(CVI_MIPI_IOC_MAGIC, 0x21, struct manual_wdr_s)

【参数】

struct manual_wdr_s

【返回值】

返回值 |

描述 |

|---|---|

0 |

成功 |

-1 |

失败,并设置errno |

【处理器差异】

无

【需求】

头文件: cvi_vip_cif.h

【注意】

无

2.4.10. CVI_MIPI_SET_LVDS_FP_VS¶

【描述】

设定sub-LVDS中VSYNC生成的时间点。

【定义】

#define CVI_MIPI _SET_LVDS_FP_VS _IOW(CVI_MIPI_IOC_MAGIC, 0x22, struct vsync_gen_s)

【参数】

struct vsync_gen_s

【返回值】

返回值 |

描述 |

|---|---|

0 |

成功 |

-1 |

失败,并设置errno |

【处理器差异】

无

【需求】

头文件: cvi_vip_cif.h

【注意】

无

2.4.11. CVI_VIP_MIPI_TX_SET_DEV_CFG¶

【描述】

设置MIPI Tx设备的属性。

【定义】

#define CVI_VIP_MIPI_TX_SET_DEV_CFG _IOW(CVI_VIP_MIPI_TX_IOC_MAGIC, 0x01, struct combo_dev_cfg_s)

【参数】

MIPI Tx设备属性结构体,详见combo_dev_cfg_s结构体说明。

【返回值】

返回值 |

描述 |

|---|---|

0 |

成功 |

-1 |

失败,并设置errno |

【处理器差异】

无

【需求】

头文件: cvi_mipi_tx.h

【注意】

无

2.4.12. MSG_CMD_MIPI_TX_SET_DEV_CFG¶

该双系统命令的描述、参数、返回值、处理器差异、需求、注意项皆与单系统命令CVI_VIP_MIPI_TX_SET_DEV_CFG相同。

【定义】

typedef enum tagMSG_MIPI_TX_CMD_E {

MSG_CMD_MIPI_TX_SET_DEV_CFG = 0,

MSG_CMD_MIPI_TX_SET_CMD,

MSG_CMD_MIPI_TX_GET_CMD,

MSG_CMD_MIPI_TX_ENABLE,

MSG_CMD_MIPI_TX_DISABLE,

MSG_CMD_MIPI_TX_SET_HS_SETTLE,

MSG_CMD_MIPI_TX_GET_HS_SETTLE,

MSG_CMD_MIPI_TX_BUFF

} MSG_MIPI_TX_CMD_E;

双系统后续命令的定义都来自该枚举,不再叙述。

2.4.13. CVI_VIP_MIPI_TX_GET_CMD¶

【描述】

从MIPI Tx设备读取信息。

【定义】

#define CVI_VIP_MIPI_TX_GET_CMD _IOWR(CVI_VIP_MIPI_TX_IOC_MAGIC, 0x04, struct get_cmd_info_s)

【参数】

详见get_cmd_info_s结构体说明

【返回值】

返回值 |

描述 |

|---|---|

0 |

成功 |

-1 |

失败,并设置errno |

【处理器差异】

无

【需求】

头文件: cvi_mipi_tx.h

【注意】

无

2.4.14. MSG_CMD_MIPI_TX_GET_CMD¶

该双系统命令的描述、参数、返回值、处理器差异、需求、注意项皆与单系统命令CVI_VIP_MIPI_TX_GET_CMD相同。

【定义】

见MSG_CMD_MIPI_TX_SET_DEV_CFG命令的定义说明。

2.4.15. CVI_VIP_MIPI_TX_SET_CMD¶

【描述】

设备发送命令给MIPI Tx设备。

【定义】

单系统:

#define CVI_VIP_MIPI_TX_SET_CMD _IOW(CVI_VIP_MIPI_TX_IOC_MAGIC, 0x02, struct cmd_info_s)

【参数】

详见cmd_info_s 结构体说明。

【返回值】

返回值 |

描述 |

|---|---|

0 |

成功 |

-1 |

失败,并设置errno |

【处理器差异】

无

【需求】

头文件: cvi_mipi_tx.h

【注意】

无

2.4.16. MSG_CMD_MIPI_TX_SET_CMD¶

该双系统命令的描述、参数、返回值、处理器差异、需求、注意项皆与单系统命令CVI_VIP_MIPI_TX_SET_CMD相同。

【定义】

见MSG_CMD_MIPI_TX_SET_DEV_CFG命令的定义说明。

2.4.17. CVI_VIP_MIPI_TX_ENABLE¶

【描述】

启用MIPI Tx设备。

【定义】

#define CVI_VIP_MIPI_TX_ENABLE _IO(CVI_VIP_MIPI_TX_IOC_MAGIC, 0x03)

【参数】

无

【返回值】

返回值 |

描述 |

|---|---|

0 |

成功 |

-1 |

失败,并设置errno |

【处理器差异】

无

【需求】

头文件: cvi_mipi_tx.h

【注意】

无

2.4.18. MSG_CMD_MIPI_TX_ENABLE¶

该双系统命令的描述、参数、返回值、处理器差异、需求、注意项皆与单系统命令CVI_VIP_MIPI_TX_ENABLE相同。

【定义】

见MSG_CMD_MIPI_TX_SET_DEV_CFG命令的定义说明。

2.4.19. CVI_VIP_MIPI_TX_DISABLE¶

【描述】

禁用MIPI Tx设备。

【定义】

#define CVI_VIP_MIPI_TX_DISABLE _IO(CVI_VIP_MIPI_TX_IOC_MAGIC, 0x05)

【参数】

无

【返回值】

返回值 |

描述 |

|---|---|

0 |

成功 |

-1 |

失败,并设置errno |

【处理器差异】

无

【需求】

头文件: cvi_mipi_tx.h

【注意】

无

2.4.20. MSG_CMD_MIPI_TX_DISABLE¶

该双系统命令的描述、参数、返回值、处理器差异、需求、注意项皆与单系统命令CVI_VIP_MIPI_TX_DISABLE相同。

【定义】

见MSG_CMD_MIPI_TX_SET_DEV_CFG命令的定义说明。

2.4.21. CVI_VIP_MIPI_TX_SET_HS_SETTLE¶

【描述】

设定MIPI Tx在HS mode下的settle timing。

【定义】

#define CVI_VIP_MIPI_TX_SET_HS_SETTLE _IOW(CVI_VIP_MIPI_TX_IOC_MAGIC, 0x06, struct hs_settle_s)

【参数】

详见hs_settle_s结构体说明。

【返回值】

返回值 |

描述 |

|---|---|

0 |

成功 |

-1 |

失败,并设置errno |

【处理器差异】

无

【需求】

头文件: cvi_mipi_tx.h

【注意】

2.4.22. MSG_CMD_MIPI_TX_SET_HS_SETTLE¶

该双系统命令的描述、参数、返回值、处理器差异、需求、注意项皆与单系统命令CVI_VIP_MIPI_TX_SET_HS_SETTLE相同。

【定义】

见MSG_CMD_MIPI_TX_SET_DEV_CFG命令的定义说明。

2.4.23. CVI_VIP_MIPI_TX_GET_HS_SETTLE¶

【描述】

取得MIPI Tx在HS mode下的settle timing。

【定义】

#define CVI_VIP_MIPI_TX_GET_HS_SETTLE _IOWR(CVI_VIP_MIPI_TX_IOC_MAGIC, 0x06, struct hs_settle_s)

【参数】

详见hs_settle_s结构体说明。

【返回值】

返回值 |

描述 |

|---|---|

0 |

成功 |

-1 |

失败,并设置errno |

【处理器差异】

无

【需求】

头文件: cvi_mipi_tx.h

【注意】

2.4.24. MSG_CMD_MIPI_TX_GET_HS_SETTLE¶

该双系统命令的描述、参数、返回值、处理器差异、需求、注意项皆与单系统命令CVI_VIP_MIPI_TX_GET_HS_SETTLE相同。

【定义】

见MSG_CMD_MIPI_TX_SET_DEV_CFG命令的定义说明。

2.5. 数据类型¶

MIPI RX相关数据类型定义如下:

CVI_MIPI_IOC_MAGIC :MIPI Rx ioctl命令的幻数。

MIPI_LANE_NUM :MIPI Rx的MIPI设备支持的最大Lane数。

WDR_VC_NUM :定义最多支持的Virtual Channel数量。

SYNC_CODE_NUM :定义LVDS每个Virtual Channel的同步码数量。

input_mode_e :MIPI Rx输入接口类型。

img_size_s :MIPI Rx输入数据每帧的大小。

rx_mac_clk_e :MAC 的支持工作时钟。

cam_pll_freq_e :MIPI-RX输出的Sensor参考时钟。

mclk_pll_s :MIPI-RX输出的Sensor参考时钟设定。

raw_data_type_e :MIPI Rx输入数据格式。

mipi_wdr_mode_e :MIPI-CSI WDR模式。

wdr_mode_e :LVDS/HISPI WDR模式。

lvds_sync_mode_e :LVDS同步模式。

lvds_bit_endian :比特位大小端模式。

lvds_vsync_type_e :LVDS 在WDR模式的同步方式。

lvds_fid_type_e :LVDS frame identification ID类型

lvds_vsync_type_s: LVDS WDR同步参数

lvds_dev_attr_s: SubLVDS/HiSPi设备属性

dphy_s: MIPI DPHY 属性

mipi_demux_info_s: MIPI解多任务模式属性

mipi_dev_attr_s: MIPI-CSI设备属性

manual_wdr_attr_s: 手动WDR模式参数

ttl_pin_func_e: TTL/BT接口的配置功能

ttl_src_e: TTL/BT接口输入来源

bt_demux_mode_e: BT解多任务模式的信道数量

bt_demux_sync_s: BT解多任务模式的同步码配置

bt_demux_attr_s: BT解多任务模式的设备属性

ttl_dev_attr_s: TTL/BT设备属性

combo_dev_attr_s: combo 设备属性

crop_top_s: 舍弃开头的行数据属性

manual_wdr_s: 手动WDR模式设定

vsync_gen_s: SUBLVDS垂直同步信号属性

MIPI TX相关数据类型定义如下:

LANE_MAX_NUM: 一个MIPI Tx设备支持的最大Lane数

output_mode_e: MIPI Tx输出模式

video_mode_e: MIPI Tx视频模式

output_format_e: MIPI Tx输出格式

sync_info_s: MIPI Tx设备同步信息

combo_dev_cfg_s: MIPI Tx设备属性

cmd_info_s: 从MIPI Tx设备取回信息

get_cmd_info_s: 从MIPI Tx设备取回信息

hs_settle_s: MIPI Tx设备HS mode下的settle信息

2.5.1. CVI_MIPI_IOC_MAGIC¶

【说明】

MIPI Rx ioctl命令的幻数

【定义】

#define CVI_MIPI_IOC_MAGIC 'm'

【处理器差异】

无。

【注意事项】

无。

【相关数据类型及接口】

无

2.5.2. MIPI_LANE_NUM¶

【说明】

一个MIPI Rx设备支持的最大Lane数。

【定义】

#define MIPI_LANE_NUM 4

【处理器差异】

无。

【注意事项】

无。

【相关数据类型及接口】

无

2.5.3. WDR_VC_NUM¶

【说明】

定义最多支持的Virtual Channel数量

【定义】

#define WDR_VC_NUM 2

【处理器差异】

无。

【注意事项】

无。

【相关数据类型及接口】

无

2.5.4. SYNC_CODE_NUM¶

【说明】

定义LVDS每个Virtual Channel的同步码数量。

【定义】

#define SYNC_CODE_NUM 4

【处理器差异】

无。

【注意事项】

无。

【相关数据类型及接口】

无

2.5.5. BT_DEMUX_NUM¶

【说明】

定义使用bt demux功能时支持最大的信道数量。

【定义】

#define BT_DEMUX_NUM 4

【处理器差异】

无。

【注意事项】

无。

【相关数据类型及接口】

无

2.5.6. MIPI_DEMUX_NUM¶

【说明】

定义使用mipi demux功能时支持最大的virtual channel数量。

【定义】

#define MIPI_DEMUX_NUM 4

【处理器差异】

无。

【注意事项】

无。

【相关数据类型及接口】

无

2.5.7. input_mode_e¶

【说明】

MIPI Rx输入接口类型。

【定义】

enum input_mode_e

{

INPUT_MODE_MIPI = 0,

INPUT_MODE_SUBLVDS,

INPUT_MODE_HISPI,

INPUT_MODE_CMOS,

INPUT_MODE_BT1120,

INPUT_MODE_BT601_19B_VHS,

INPUT_MODE_BT656_9B,

INPUT_MODE_CUSTOM_0,

INPUT_MODE_BT_DEMUX,

INPUT_MODE_BUTT

};

【处理器差异】

无。

【注意事项】

无。

【相关数据类型及接口】

无

2.5.8. img_size_s¶

【说明】

MIPI Rx输入数据每帧的大小。

【定义】

struct img_size_s {

unsigned int width;

unsigned int height;

};

【处理器差异】

无。

【注意事项】

无。

【相关数据类型及接口】

无

2.5.9. rx_mac_clk_e¶

【说明】

MAC 的支持工作时钟。

【定义】

enum rx_mac_clk_e {

RX_MAC_CLK_200M = 0,

RX_MAC_CLK_400M,

RX_MAC_CLK_500M,

RX_MAC_CLK_600M,

RX_MAC_CLK_BUTT,

};

【处理器差异】

无。

【注意事项】

MAC时钟与支持的MIPI时钟关系请参考1.7.2。

【相关数据类型及接口】

无

2.5.10. cam_pll_freq_e¶

【说明】

MIPI-RX输出的Sensor参考时钟。

【定义】

enum cam_pll_freq_e {

CAMPLL_FREQ_NONE = 0,

CAMPLL_FREQ_37P125M,

CAMPLL_FREQ_25M,

CAMPLL_FREQ_27M,

CAMPLL_FREQ_24M,

CAMPLL_FREQ_26M,

CAMPLL_FREQ_NUM

};

【处理器差异】

无。

【注意事项】

无。

【相关数据类型及接口】

无

2.5.11. mclk_pll_s¶

【说明】

MIPI-RX输出的Sensor参考时钟设定。

【定义】

struct mclk_pll_s {

unsigned int cam;

enum cam_pll_freq_e freq;

};

【成员】

成员 |

描述 |

|---|---|

cam |

0: 输出为CAM_MCLK0 1: 输出为CAM_MCLK1 |

freq |

输出的Sensor参考时钟 |

【处理器差异】

无。

【注意事项】

无。

【相关数据类型及接口】

无

2.5.12. raw_data_type_e¶

【说明】

MIPI Rx输入数据格式。

【定义】

enum raw_data_type_e {

RAW_DATA_8BIT = 0,

RAW_DATA_10BIT,

RAW_DATA_12BIT,

YUV422_8BIT, /* MIPI-CSI only */

YUV422_10BIT, /* MIPI-CSI only*/

RAW_DATA_BUTT

};

【处理器差异】

无。

【注意事项】

YUV422_8BIT与YUV422_10BIT只支持MIPI-CSI格式。

【相关数据类型及接口】

无

2.5.13. mipi_wdr_mode_e¶

【说明】

MIPI-CSI WDR模式。

【定义】

enum mipi_wdr_mode_e {

CVI_MIPI_WDR_MODE_NONE = 0,

CVI_MIPI_WDR_MODE_VC,

CVI_MIPI_WDR_MODE_DT,

CVI_MIPI_WDR_MODE_DOL,

CVI_MIPI_WDR_MODE_MANUAL, /* SOI case */

CVI_MIPI_WDR_MODE_BUTT

};

【成员】

成员 |

描述 |

|---|---|

CVI_MIPI_WDR_MODE_NONE |

线性模式 |

CVI_MIPI_WDR_MODE_VC |

MIPI-CSI Virtual Channel模式 |

CVI_MIPI_WDR_MODE_DT |

MIPI-CSI Data Type模式 |

CVI_MIPI_WDR_MODE_DOL |

Sony DOL LI模式 |

CVI_MIPI_WDR_MODE_MANUAL |

WDR手动模式 |

【处理器差异】

无。

【注意事项】

CVI_MIPI_WDR_MODE_VC适用于使用MIPI-CSI Virtual Channel ID分辨长曝线与短曝线的Sensor。

CVI_MIPI_WDR_MODE_DT适用于使用MIPI-CSI Data Type ID分辨长曝线与短曝线的Sensor。 注意注意长曝与短曝必须在同一帧开始与结束。

CVI_MIPI_WDR_MODE_DOL适用于使用SONY MIPI-CSI Line Information模式。

CVI_MIPI_WDR_MODE_MANUAL使用自定义的规则决定长曝线与短曝线。

【相关数据类型及接口】

无

2.5.14. wdr_mode_e¶

【说明】

Sub-LVDS/HISPI WDR模式。

【定义】

enum wdr_mode_e {

CVI_WDR_MODE_NONE = 0,

CVI_WDR_MODE_2F,

CVI_WDR_MODE_3F,

CVI_WDR_MODE_DOL_2F,

CVI_WDR_MODE_DOL_3F,

CVI_WDR_MODE_DOL_BUTT

};

【成员】

成员 |

描述 |

|---|---|

CVI_WDR_MODE_NONE |

线性模式 |

CVI_WDR_MODE_2F |

一般双曝WDR |

CVI_WDR_MODE_3F |

一般三曝WDR |

CVI_WDR_MODE_DOL_2F |

Sony DOL-2 WDR |

CVI_WDR_MODE_DOL_3F |

Sony DOL-3 WDR |

【处理器差异】

无。

【注意事项】

CVI_WDR_MODE_2F适用于一般MIPI-CSI/HiSPi的交错式WDR。

CVI_WDR_MODE_DOL_2F适合用Sony Sub-LVDS DOL-2 WDR

CV181x不支援CVI_WDR_MODE_3F与CVI_WDR_MODE_DOL_3

CV180X不支持WDR mode

【相关数据类型及接口】

无

2.5.15. lvds_sync_mode_e¶

【说明】

LVDS同步模式。

【定义】

enum lvds_sync_mode_e {

LVDS_SYNC_MODE_SOF = 0,

LVDS_SYNC_MODE_SAV,

LVDS_SYNC_MODE_BUTT

};

【成员】

成员 |

描述 |

|---|---|

LVDS_SYNC_MODE_SOF |

SOF, EOF, SOL, EOL。 请参考图1-1 |

LVDS_SYNC_MODE_SAV |

Invalid SAV, invalid EAV, valid SAV, valid EAV。 请参考图1-2 |

【处理器差异】

无。

【注意事项】

LVDS_SYNC_MODE_SOF适用于HiSPi Packetize-SP模式。

LVDS_SYNC_MODE_SAV适用于sub-LVDS与HiSPi Streaming-SP模式

当输入为INPUT_MODE_HISPI并且同步模式为LVDS_SYNC_MODE_SAV。 MIPI-Rx切换到HiSPi Streaming-SP模式。

【相关数据类型及接口】

无

2.5.16. lvds_bit_endian¶

【说明】

比特位大小端模式。

【定义】

enum lvds_bit_endian {

LVDS_ENDIAN_LITTLE = 0,

LVDS_ENDIAN_BIG,

LVDS_ENDIAN_BUTT

};

【处理器差异】

无。

【注意事项】

无。

【相关数据类型及接口】

无

2.5.17. lvds_vsync_type_e¶

【说明】

LVDS 在WDR模式的同步方式。

【定义】

enum lvds_vsync_type_e {

LVDS_VSYNC_NORMAL = 0,

LVDS_VSYNC_SHARE,

LVDS_VSYNC_HCONNECT,

LVDS_VSYNC_BUTT

};

【成员】

成员 |

描述 |

|---|---|

LVDS_VSYNC_NORMAL |

长短曝光帧有独立的SOF-EOF, SOL-EOL或invalid-SAV-invalid-EAV, valid SAV-valid EAV。 |

LVDS_VSYNC_SHARE |

长短曝光帧共享一对SOF-EOF标识,短曝光的起始几行用固定值填充。 |

LVDS_VSYNC_HCONNECT |

长短曝光帧共享一对SAV-EAV标识,长短曝光帧之间是固定周期的消隐。 |

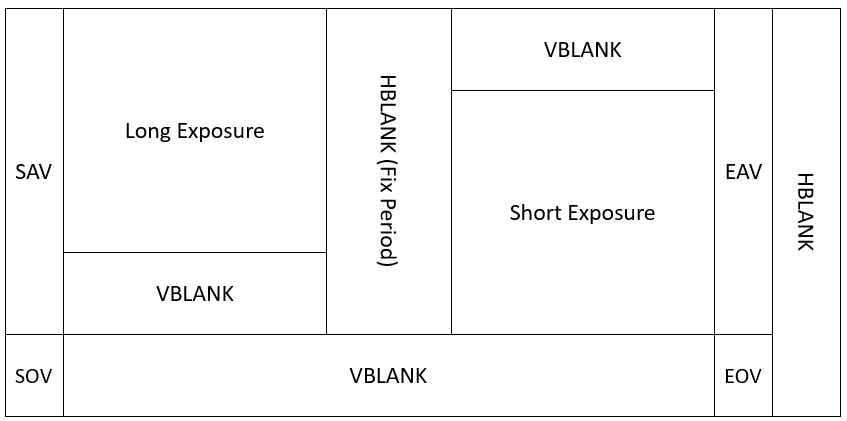

图 1‑3 LVDS_VSYNC_NORMAL同步方式.

图 1‑4 LVDS_VSYNC_HCONNECT同步方式.

【处理器差异】

无。

【注意事项】

LVDS_VSYNC_NORMAL适用于SONY sub-LVDS DOL-2 pattern 1与HiSPi Packtized-SP WDR模式。

LVDS_VSYNC_SHARE适用于HiSPi Streaming-SP WDR模式。

LVDS_VSYNC_HCONNECT适用于SONY sub-LVDS DOL-2 pattern 2。

【相关数据类型及接口】

无

2.5.18. lvds_fid_type_e¶

【说明】

LVDS frame identification ID类型。

【定义】

enum lvds_fid_type_e {

LVDS_FID_NONE = 0,

LVDS_FID_IN_SAV,

LVDS_FID_BUTT,

};

【成员】

成员 |

描述 |

|---|---|

LVDS_FID_NONE |

不使用frame identification id。 |

LVDS_FID_IN_SAV |

FID插入在SAV第4个字段中。 |

【处理器差异】

无。

【注意事项】

无

【相关数据类型及接口】

无

2.5.19. lvds_fid_type_s¶

【说明】

LVDS frame identification ID类型。

【定义】

struct lvds_fid_type_s {

enum lvds_fid_type_e fid;

};

【成员】

成员 |

描述 |

|---|---|

fid |

LVDS DOL模式下的frame identification类型 |

【处理器差异】

无。

【注意事项】

无

【相关数据类型及接口】

无

2.5.20. lvds_vsync_type_s¶

【说明】

LVDS WDR同步参数。

【定义】

struct lvds_vsync_type_s {

enum lvds_vsync_type_e sync_type;

unsigned short hblank1;

unsigned short hblank2;

};

【处理器差异】

无。

【注意事项】

当sync_type为LVDS_VSYNC_HCONNECT时, 需要配置hblank1和hblank2,表示长短曝间的消隠区长度。

【相关数据类型及接口】

无

2.5.21. lvds_dev_attr_s¶

【说明】

LVDS/SubLVDS/HiSPi设备属性。

【定义】

struct lvds_dev_attr_s {

enum wdr_mode_e wdr_mode;

enum lvds_sync_mode_e sync_mode;

enum raw_data_type_e raw_data_type;

enum lvds_bit_endian data_endian;

enum lvds_bit_endian sync_code_endian;

short lane_id[MIPI_LANE_NUM+1];

short sync_code[MIPI_LANE_NUM][WDR_VC_NUM+1][SYNC_CODE_NUM];

struct lvds_vsync_type_s vsync_type;

struct lvds_fid_type_s fid_type;

char pn_swap[MIPI_LANE_NUM+1];

};

【成员】

成员 |

描述 |

|---|---|

wdr_mode |

WDR模式 |

sync_mode |

LVDS同步模式 |

raw_data_type |

传输的数据类型 |

data_endian |

数据大小端模式 |

sync_code_endian |

同步码大小端模式 |

lane_id |

发送端(sensor)和接收端(MIPI Rx) lane的对应关系 |

sync_code |

每个Virtual Channel有4个同步码,根据同步模式不同,分别表示SOF/EOF/ SOL/EOL的同步码或者invalid SAV/invalid EAV/ valid SAV/valid EAV的同步码。 |

vsync_type |

vsync类型,当wdr_mod为DOL模式并且sync_mode为LVDS_SYNC_MODE_SAV时,需要配置vsync的类型。 |

fid_type |

frame identification类型 |

pn_swap |

Positive/negative line 是否交换 |

【处理器差异】

无。

【注意事项】

无

【相关数据类型及接口】

无

2.5.22. dphy_s¶

【说明】

MIPI RX DPHY 属性。

【定义】

struct mipi_dev_attr_s {

unsigned char enable;

unsigned char hs_settle;

};

【成员】

成员 |

描述 |

|---|---|

enable |

开启MIPI RX DPHY属性设定 |

hs_settle |

hs settle time |

【处理器差异】

无。

【注意事项】

无

【相关数据类型及接口】

无

2.5.23. mipi_demux_info_s¶

【说明】

MIPI CSI使用Virtual Channel 解多任务的属性设定。

【定义】

struct mipi_demux_info_s {

unsigned int demux_en;

unsigned char vc_mapping[MIPI_DEMUX_NUM];

};

【成员】

成员 |

描述 |

|---|---|

demux_en |

开启mipi virtual channel 解多任务 |

vc_mapping |

设定ISP channel 与mipi virtual channel对应关系. 例如vc_mapping = {0, 2, 3, 1}, ISP ch0代表vc=0; ch1代表vc=2; ch2代表vc=3; ch3代表vc=1. |

【处理器差异】

无。

【注意事项】

无

【相关数据类型及接口】

无

2.5.24. mipi_dev_attr_s¶

【说明】

MIPI-CSI设备属性。

【定义】

struct mipi_dev_attr_s {

enum raw_data_type_e raw_data_type;

short lane_id[MIPI_LANE_NUM+1];

enum mipi_wdr_mode_e wdr_mode;

short data_type[WDR_VC_NUM];

char pn_swap[MIPI_LANE_NUM+1];

};

【成员】

成员 |

描述 |

|---|---|

wdr_mode |

WDR模式 |

raw_data_type |

传输的数据类型 |

lane_id |

发送端(sensor)和接收端(MIPI Rx) lane的对应关系 |

data_type |

当WDR模式为CVI_MIPI_WDR_MODE_DT时, 每个WDR frames对应的data type。 |

pn_swap |

Positive/negative line 是否交换。 |

【处理器差异】

无。

【注意事项】

无

【相关数据类型及接口】

无

2.5.25. manaul_wdr_attr_s¶

【说明】

手动WDR模式参数。

【定义】

struct manaul_wdr_attr_s {

unsigned int manual_en;

unsigned short l2s_distance;

unsigned short lsef_length;

unsigned int discard_padding_lines;

unsigned int update;

};

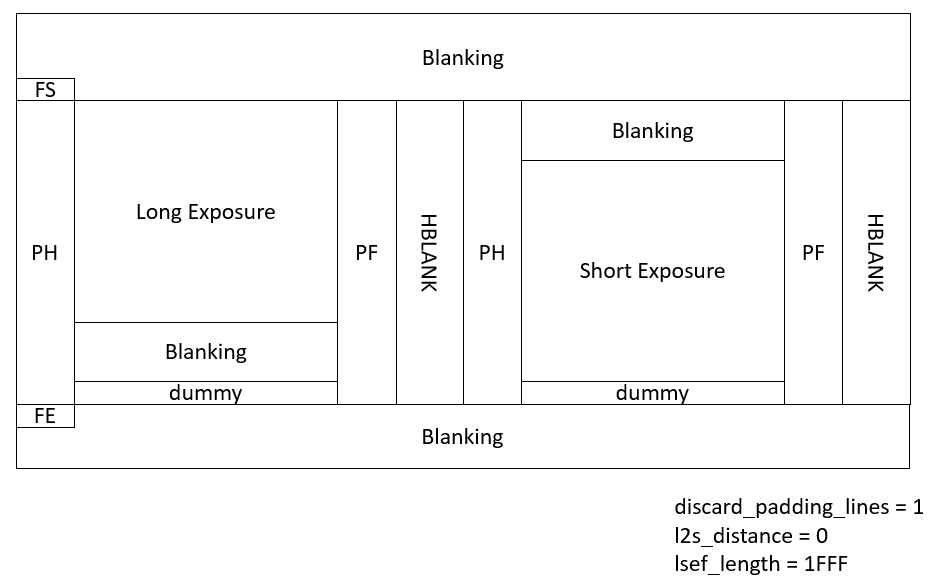

【成员】

成员 |

描述 |

|---|---|

manual_en |

手动WDR开关 |

l2s_distance |

一帧中首条长曝到首列短曝的距离, 单位为行数。 |

lsef_length |

长曝/短曝的行数。 |

discard_padding_lines |

Sensor是否有把padding行当有效行输出。 |

update |

是否强制更新设定。 若否, 设定会等下一张的同步讯号来才更新。 |

【处理器差异】

无。

【注意事项】

HiSPi输入并且sync_type为LVDS_VSYNC_SHARE时,需打开手动WDR模式并设定参数。

MIPI-CSI输入并且wdr mode为CVI_MIPI_WDR_MODE_MANUAL时,需打开手动WDR模式并设定参数。

【相关数据类型及接口】

无

2.5.26. ttl_pin_func_e¶

【说明】

TTL/BT接口的配置功能.

【定义】

enum ttl_pin_func_e {

TTL_PIN_FUNC_VS,

TTL_PIN_FUNC_HS,

TTL_PIN_FUNC_VDE,

TTL_PIN_FUNC_HDE,

TTL_PIN_FUNC_D0,

TTL_PIN_FUNC_D1,

TTL_PIN_FUNC_D2,

TTL_PIN_FUNC_D3,

TTL_PIN_FUNC_D4,

TTL_PIN_FUNC_D5,

TTL_PIN_FUNC_D6,

TTL_PIN_FUNC_D7,

TTL_PIN_FUNC_D8,

TTL_PIN_FUNC_D9,

TTL_PIN_FUNC_D10,

TTL_PIN_FUNC_D11,

TTL_PIN_FUNC_D12,

TTL_PIN_FUNC_D13,

TTL_PIN_FUNC_D14,

TTL_PIN_FUNC_D15,

TTL_PIN_FUNC_NUM,

};

【处理器差异】

无。

【注意事项】

无

【相关数据类型及接口】

无

2.5.27. ttl_src_e¶

【说明】

TTL/BT接口输入来源.

【定义】

enum ttl_src_e {

TTL_VI_SRC_VI0 = 0,

TTL_VI_SRC_VI1,

TTL_VI_SRC_VI2, /* BT demux */

TTL_VI_SRC_NUM

};

【处理器差异】

无。

【注意事项】

无

【相关数据类型及接口】

参考表1-1.

2.5.28. bt_demux_mode_e¶

【说明】

BT解多任务模式的信道数量。

【定义】

enum bt_demux_mode_e {

BT_DEMUX_DISABLE = 0,

BT_DEMUX_2,

BT_DEMUX_3,

BT_DEMUX_4,

};

【处理器差异】

无。

【注意事项】

无

【相关数据类型及接口】

无

2.5.29. bt_demux_sync_s¶

【说明】

BT解多任务模式的同步码设定。

【定义】

struct bt_demux_sync_s {

unsigned char sav_vld;

unsigned char sav_blk;

unsigned char eav_vld;

unsigned char eav_blk;

};

【成员】

成员 |

描述 |

|---|---|

sav_vld |

有效数据区间的SAV |

sav_blk |

空白区间的SAV |

eav_vld |

有效数据区间的EAV |

eav_blk |

空白区间的EAV |

【处理器差异】

无。

【注意事项】

无

【相关数据类型及接口】

无

2.5.30. bt_demux_attr_s¶

【说明】

BT解多任务模式的属性设定。

【定义】

struct bt_demux_attr_s {

signed char func[TTL_PIN_FUNC_NUM];

unsigned short v_fp;

unsigned short h_fp;

unsigned short v_bp;

unsigned short h_bp;

enum bt_demux_mode_e mode;

unsigned char sync_code_part_A[3]; /* sync code 0~2 */

struct bt_demux_sync_s sync_code_part_B[BT_DEMUX_NUM]; /* sync code 3 */

char yc_exchg;

};

【成员】

成员 |

描述 |

|---|---|

func |

BT接口对应输入源TTL_VI_SRC_VI2的lane number. Index为BT逻辑功能, value请参考表1-1. 例如, func[TTL_PIN_FUNC_D0] = 5, 代表BT讯号的D0接到VI2_D[5], 即pad name VIVO_D5。 |

v_fp |

垂直方向的front porch |

h_fp |

水平方向的front porch |

v_bp |

垂直方向的back porch |

h_bp |

水平方向的back porch |

mode |

BT解多任务模式的信道数量 |

sync_code_part_A |

BT解多任务模式的0~2同步码 |

sync_code_part_B |

BT解多任务模式的同步码3 |

yc_exchg |

BIT0~BIT3分别代表CH0~CH3的Y Cb/Cr bytes顺序互换. 1 为互换, 0 为不互换. |

【处理器差异】

无。

【注意事项】

无

【相关数据类型及接口】

无

2.5.31. ttl_dev_attr_s¶

【说明】

TTL/BT接口的属性设定。

【定义】

struct ttl_dev_attr_s {

enum ttl_src_e vi;

signed char func[TTL_PIN_FUNC_NUM];

unsigned short v_bp;

unsigned short h_bp;

};

【成员】

成员 |

描述 |

|---|---|

vi |

TTL/BT接口的输入来源, 允许值为TTL_VI_SRC_VI0或TTL_VI_SRC_VI1 |

func |

BT接口对应输入源的lane number. Index为BT逻辑功能, value请参考表1-1. 例如, vi = TTL_VI_SRC_VI1时, func[TTL_PIN_FUNC_D0] = 5, 代表BT讯号的D0接到VI1_D[5], 即pad name VIVO_D5. |

v_bp |

垂直方向的back porch |

h_bp |

水平方向的back porch |

【处理器差异】

无。

【注意事项】

无

【相关数据类型及接口】

无

2.5.32. combo_dev_attr_s¶

【说明】

combo 设备属性,由于MIPI Rx能够对接CSI-2,sub-LVDS,HiSPi等时序,所以将MIPI Rx称为combo设备。

【定义】

struct combo_dev_attr_s {

enum input_mode_e input_mode;

enum rx_mac_clk_e mac_clk;

struct mclk_pll_s mclk;

union {

struct mipi_dev_attr_s mipi_attr;

struct lvds_dev_attr_s lvds_attr;

struct ttl_dev_attr_s ttl_attr;

struct bt_demux_attr_s bt_demux_attr;

};

unsigned int devno;

struct img_size_s img_size;

struct manaul_wdr_attr_s wdr_manu;

};

【成员】

成员 |

描述 |

|---|---|

input_mode |

输入接口类型 |

mac_clk |

MIPI RX MAC时钟设定 |

mclk |

MIPI RX输出的Sensor参考时钟设定 |

mipi_attr |

如果input_mode配置为INPUT_MODE_MIPI, 则必须配置mipi_attr |

lvds_attr |

如果input_mode配置为INPUT_MODE_SUBLVDS/INPUT_MODE_HISPI, 则必须配置lvds_attr |

devno |

MIPI-Rx设备号 |

img_size |

输入帧大小 |

wdr_manu |

手动WDR属性 |

【处理器差异】

无。

【注意事项】

无

【相关数据类型及接口】

无

2.5.33. crop_top_s¶

【说明】

舍弃开头的行资料。

【定义】

struct crop_top_s {

unsigned int devno;

unsigned int crop_top;

unsigned int update;

};

【成员】

成员 |

描述 |

|---|---|

devno |

MIPI-Rx设备号 |

crop_top |

开头要拾弃的行数 |

update |

是否强制更新设定。 若否, 设定会等下一张的同步讯号来才更新。 |

【处理器差异】

无。

【注意事项】

无

【相关数据类型及接口】

无

2.5.34. manual_wdr_s¶

【说明】

手动WDR模式设定。

【定义】

struct manual_wdr_s {

unsigned int devno;

struct manaul_wdr_attr_s attr;

};

【成员】

成员 |

描述 |

|---|---|

devno |

MIPI-Rx设备号 |

attr |

手动WDR属性 |

【处理器差异】

无。

【注意事项】

无

【相关数据类型及接口】

无

2.5.35. vsync_gen_s¶

【说明】

手动WDR模式设定。

【定义】

struct vsync_gen_s {

unsigned int devno;

unsigned int distance_fp;

};

【成员】

成员 |

描述 |

|---|---|

devno |

MIPI-Rx设备号 |

distance_fp |

当input_mode为INPUT_MODE_SUBLVDS时,产生垂直同步信号的时间点。 |

【处理器差异】

无。

【注意事项】

Sub-LVDS不自带垂直同步信号,所以MIPI-Rx须自行生成送给ISP。 distance_fp 可调整垂直同步时间点以达到加大front porch的作用。

【相关数据类型及接口】

无

2.5.36. LANE_MAX_NUM¶

【说明】

一个MIPI Tx设备支持的最大Lane数。

【定义】

#define MIPI_LANE_NUM 4

【处理器差异】

无。

【注意事项】

无

【相关数据类型及接口】

无

2.5.37. output_mode_e¶

【说明】

MIPI Tx输出模式。

【定义】

enum output_mode_e

{

OUTPUT_MODE_CSI = 0x0, /* csi mode */ OUTPUT_MODE_DSI_VIDEO = 0x1, /* dsi video mode */

OUTPUT_MODE_DSI_CMD = 0x2, /* dsi command mode */

OUTPUT_MODE_BUTT

} output_mode_t;

【处理器差异】

无

【注意事项】

无

【相关数据类型及接口】

无

2.5.38. video_mode_e¶

【说明】

MIPI Tx视频模式。

【定义】

enum video_mode_e {

BURST_MODE = 0x0,

NON_BURST_MODE_SYNC_PULSES = 0x1,

NON_BURST_MODE_SYNC_EVENTS = 0x2,

};

【处理器差异】

无

【注意事项】

无

【相关数据类型及接口】

无

2.5.39. output_format_e¶

【说明】

LVDS 在WDR模式的同步方式。

【定义】

enum output_format_e {

OUT_FORMAT_RGB_16_BIT = 0x0,

OUT_FORMAT_RGB_18_BIT = 0x1,

OUT_FORMAT_RGB_24_BIT = 0x2,

OUT_FORMAT_RGB_30_BIT = 0x3,

OUT_FORMAT_YUV420_8_BIT_NORMAL = 0x4,

OUT_FORMAT_YUV420_8_BIT_LEGACY = 0x5,

OUT_FORMAT_YUV422_8_BIT = 0x6,

OUT_FORMAT_BUTT

};

【处理器差异】

处理器差异 |

是否支持 |

|---|---|

CV181x |

不支持YUV420 |

CV180x |

不支持YUV420 |

【注意事项】

无

【相关数据类型及接口】

无

2.5.40. sync_info_s¶

【说明】

MIPI Tx设备同步信息。

【定义】

struct sync_info_s {

unsigned short vid_hsa_pixels;

unsigned short vid_hbp_pixels;

unsigned short vid_hfp_pixels;

unsigned short vid_hline_pixels;

unsigned short vid_vsa_lines;

unsigned short vid_vbp_lines;

unsigned short vid_vfp_lines;

unsigned short vid_active_lines;

unsigned short edpi_cmd_size;

bool vid_vsa_pos_polarity;

bool vid_hsa_pos_polarity;

};

【成员】

成员 |

描述 |

|---|---|

vid_hsa_pixels |

Horizontal sync-pluse像素个数 |

vid_hbp_pixels |

Horizontal back-porch像素个数 |

vid_hfp_pixels |

Horizontal front-porch像素个数 |

vid_hline_pixels |

Horizontal image active像素个数 |

vid_vsa_lines |

Vertical sync-pluse行数 |

vid_hbp_pixels |

Vertical back-porch行数 |

vid_hbp_pixels |

Vertical front-porch行数 |

vid_active_pixels |

Vertical image active行数 |

edpi_cmd_size |

写内存命令字节数。video mode时该值无效,command mode时该值设为hact。 |

vid_vsa_pos_polarity; |

Horizontal sync-pluse polarity |

vid_hsa_pos_polarity; |

Vertical sync-pluse polarity |

【处理器差异】

无。

【注意事项】

无

【相关数据类型及接口】

无

2.5.41. combo_dev_cfg_s¶

【说明】

MIPI Tx设备属性。

【定义】

struct combo_dev_cfg_s {

unsigned int devno;

enum mipi_tx_lane_id lane_id[LANE_MAX_NUM];

enum output_mode_e output_mode;

enum video_mode_e video_mode;

enum output_format_e output_format;

struct sync_info_s sync_info;

unsigned int phy_data_rate;

unsigned int pixel_clk;

bool lane_pn_swap[LANE_MAX_NUM];

};

【成员】

成员 |

描述 |

|---|---|

devno |

devno |

lane_id |

发送端(vo)和接收端(MIPI Tx) Lane的对应关系;未使用的Lane设置为-1。 |

output_mode |

MIPI Tx输出模式。 |

video_mode |

MIPI Tx视频模式。 |

output_format |

MIPI Tx输出格式。 |

sync_info |

MIPI Tx设备的同步信息。 |

phy_data_rate |

MIPI Tx输出速率,MIPI Tx高速模式每个信道(lane)的速率范围的描述。 |

pixel_clk |

像素时钟。单位为KHz |

lane_pn_swap |

Lane设置上是否P/N要互换 |

【处理器差异】

无。

【注意事项】

无

【相关数据类型及接口】

2.5.42. cmd_info_s¶

【说明】

给MIPI Tx设备初始化信息。

【定义】

struct cmd_info_s {

unsigned int devno;

unsigned short data_type;

unsigned short cmd_size;

#ifdef __arm__

unsigned char *cmd;

unsigned int padding;

#else

unsigned char *cmd;

#endif

};

【成员】

成员 |

描述 |

|---|---|

devno |

MIPI Tx设备号 |

data_type |

命令数据类型 |

cmd_size |

命令数据字节数,范围:(0,128)。 |

cmd_data |

命令数据地址指针,需要用户分配。 |

【处理器差异】

无。

【注意事项】

无

【相关数据类型及接口】

2.5.43. get_cmd_info_s¶

【说明】

从MIPI Tx设备取回信息。

【定义】

struct get_cmd_info_s {

unsigned int devno;

unsigned short data_type;

unsigned short data_param;

unsigned short get_data_size;

#ifdef __arm__

unsigned int padding1;

unsigned char *get_data;

unsigned int padding2;

#else

unsigned int padding1;

unsigned char *get_data;

#endif

};

【成员】

成员 |

描述 |

|---|---|

devno |

MIPI Tx设备号 |

data_type |

命令数据类型 |

data_param |

数据参数,低八比特为第一个参数,高八比特为第二个参数、不用时填0 |

get_data_size |

预期获取的数据字节数,范围:(0,4)。 |

get_data |

获取到的数据存放地址指针,需要用户分配。 |

【处理器差异】

无。

【注意事项】

无

【相关数据类型及接口】

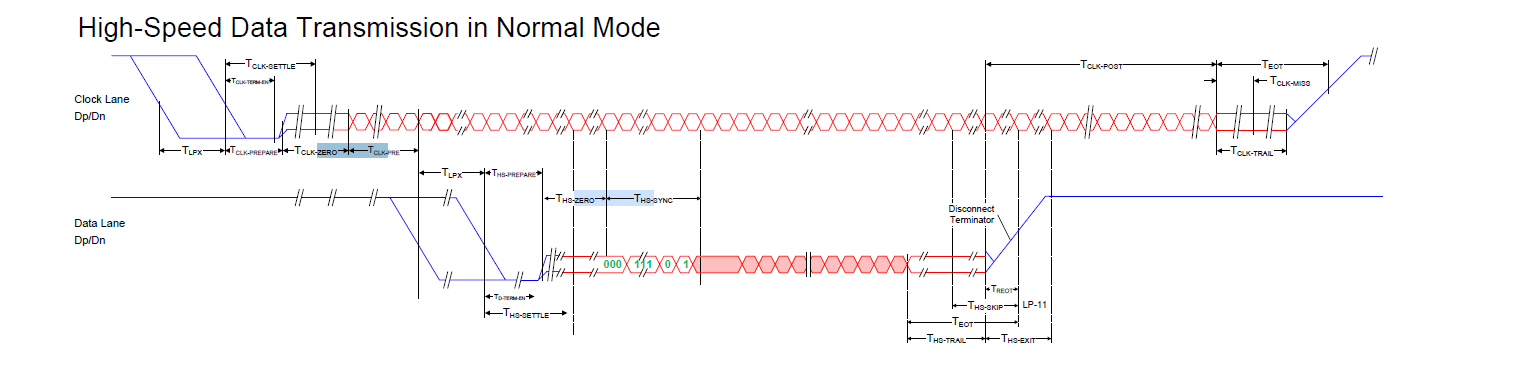

2.5.44. hs_settle_s¶

【说明】

MIPI Tx设备HS mode下的settle信息。

【定义】

struct hs_settle_s {

unsigned char prepare;

unsigned char zero;

unsigned char trail;

};

【成员】

成员 |

描述 |

|---|---|

prepare |

为LP->HS后的前置准备T数 |

zero |

在进入HS后,在输出数据前为0的T数 |

trail |

在HS->LP时,要结束HS前,数据结束后额外的T数 |

【处理器差异】

无。

【注意事项】

【相关数据类型及接口】

无

2.6. Proc信息¶

2.6.1. MIPI_RX Proc信息¶

MIPI_Rx在正常工作下proc信息中的各种错误中断计数应为0。 若否,请检查MIPI_Rx相关属性是否配置正确。

【调试信息】

Module: [MIPI_RX], Build Time[#1 SMP PREEMPT Thu Apr 29 11:18:57 CST 2021]

------------Combo DEV ATTR--------------

Devno WorkMode DataType WDRMode LinkId PN Swap SyncMode DataEndian SyncCodeEndian

0 MIPI RAW12 NONE 2, 3, 1, 4, 0 1, 1, 1, 1, 1 N/A N/A N/A

------------MIPI info-------------------

Devno EccErr CrcErr HdrErr WcErr fifofull decode

0 0 0 0 2 0 raw12

Physical: D0 D1 D2 D3 D4 D5

0 0 0 0 0 0

Digital: D0 D1 D2 D3 CK_HS CK_ULPS CK_STOP CK_ERR Deskew

hs_idle hs_idle hs_idle hs_idle 1 0 0 0 idle

【调试信息分析】

MIPI Rx通过PHY Wrapper接收Sensor的MIPI-CSI/SubLVDS/HiSPi/TTL讯号, 由MAC内对应的接口进行同步头检测与对齐。

MAC将各Lane的数据合并成Pixel数据, 并将数据发送给后级的ISP。

PHY Wrapper由sensor的pixel clock提供时钟。 MAC内的时钟与后级的ISP相同。

若要操作数据的Crop, 可由后级的ISP来调试。

图 1‑5数据示例图

【参数说明】

参数 |

描述 |

|

|---|---|---|

MIPI DEV ATTR |

Devno |

MIPI设备号 |

WorkMode |

MIPI设备工作模式: MIPI/ SUBLVDS/HISPI/CMOS等模式 |

|

DataType |

RAW8/RAW10/RAW12等类型 |

|

WDRMode |

|

|

LaneId |

Lane id |

|

PN Swap |

PN 讯号交换 |

|

LVDS DEV ATTR |

Devno |

MIPI设备号 |

WorkMode |

MIPI设备工作模式: MIPI/ SUBLVDS/HISPI/CMOS等模式 |

|

DataType |

RAW8/RAW10/RAW12等类型 |

|

WDRMode |

|

|

LaneId |

Lane id |

|

PN Swap |

PN 讯号交换 |

|

SyncMode |

|

|

DataEndian |

Data的比特位大小端模式 |

|

SyncCodeEndian |

同步码的比特位大小端模式 |

|

MIPI Info (仅MIPI模式可见) |

Devno |

MIPI设备号 |

EccErr |

ECC错误的中断计数 |

|

CrcErr |

CRC错误的中断计数 |

|

HdrErr |

HDR Flag错误的中断计数 |

|

WcErr |

Word Count错误的中断计数 |

|

fifofull |

Fifofull 的中断计数 |

|

Physical: D0 |

MIPIRX_PAD0 收到的资料 |

|

Physical: D1 |

MIPIRX_PAD1 收到的资料 |

|

Physical: D2 |

MIPIRX_PAD2 收到的资料 |

|

Physical: D3 |

MIPIRX_PAD3 收到的资料 |

|

Physical: D4 |

MIPIRX_PAD4 收到的资料 |

|

Physical: D5 |

MIPIRX_PAD5 收到的资料 |

|

Digital: D0 |

Sensor data lane 0 state |

|

Digital: D1 |

Sensor data lane 1 state |

|

Digital: D2 |

Sensor data lane 2 state |

|

Digital: D3 |

Sensor data lane 3 state |

|

CK_HS/CK_ULPS/CK_STOP/CK_ERR |

Sensor clock lane state |

|

Deskew |

Deskew 结果 |

|

2.7. FAQ¶

2.7.1. 1.6.1. Land id如何配置¶

Land id的配置对应mipi_dev_attr_s中的short lane_id[MIPI_LANE_NUM+1]或者lvds_dev_attr_s中 的short lane_id[MIPI_LANE_NUM+1],其中lane_id数组的索引号表示的是Sensor的Lane ID,索引号 0表示sensor clock,索引号1表示sensor lane 0。 land_id数组的值表示的是MIPI-Rx的Lane ID, 0表示MIPIRX1_PAD0,1表示MIPIRX1_PAD1。未使用的lane将其对应的lane_id配置为-1。

下面举例说明,例如MIPI与SENSOR的引脚硬件连接如下表所示。

SENSOR管脚 |

MIPI Lane管脚 |

|---|---|

Clock Lane (index = 0) |

MIPIRX1_PAD0 (value = 0) |

Lane 0 (index = 1) |

MIPIRX1_PAD1 (value = 1) |

Lane 1 (index = 2) |

MIPIRX1_PAD2 (value = 2) |

Lane 2 (index = 3) |

MIPIRX1_PAD3 (value = 3) |

Lane 3 (index = 4) |

MIPIRX1_PAD4 (value = 4) |

MIPI的最大Lane数加上Clock为5,所以lane_id配置如下:

//索引sensor_clk, sensor_lane0, sensor_lane1, sensor_lane2, sensor_lane3

// ↓ ↓ ↓ ↓ ↓

land_id={MIPIRX1_PAD0 MIPIRX1_PAD1 MIPIRX1_PAD2 MIPIRX1_PAD3 MIPIRX1_PAD4 }

2.7.2. MIPI频率说明¶

使用以下公式计算MIPI每Lane最高频率与VI MAC的工作频率:

MAC_Freq * pixel_width = lane_num * MIPI_Freq * 2。 其中MAC_Freq为VI MAC的工作频率,pixel_width为像素位宽,lane_num为MIPI lane个数,MIPI_Freq为每条lane的工作频率。 若MAC clock为400M,pixel_width = 12,lane_num = 4, 可支持最快MIPI_Freq = 400 * 12 / ( 4 * 2) = 600MHz。

2.7.3. Manual WDR模式使用说明¶

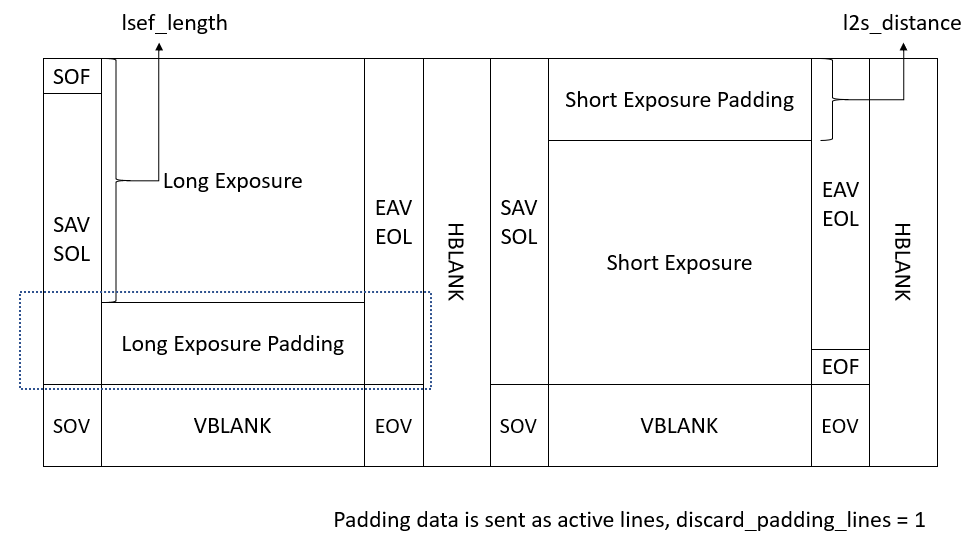

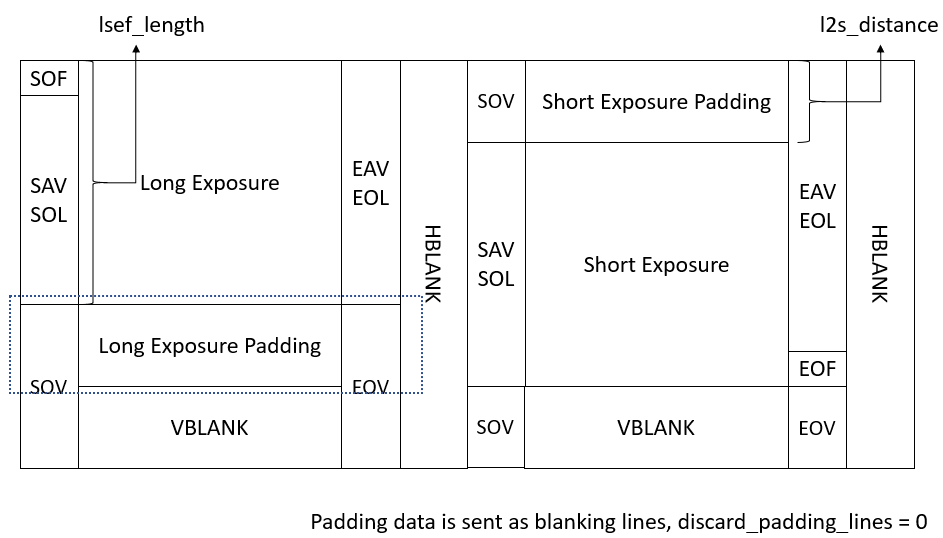

当手动WDR模式打开后,MIPI-Rx会把收下来的数据以行为单位,遵遁以下规则分配给长曝帧与短曝帧。

l2s_distance: 从第一行到第l2s_distance行都是长曝数据,第l2s_distance+1行开始长曝与短曝交错分配。

lsef_length: 第lsef_length+1行开始都是短曝帧数据。 直到下个垂直同步信号为止。

当discard_padding_lines=1时,1到l2s_distance行分配方式为{长-ignore-长-ignore …},第l2s_distance+1到lsef_length行分配方式为{长-短-长-短 …}。第lsef_length+1行到下个垂直同步信号分配方式为{短-ignore-短-ignore …}。

当discard_padding_lines=0时,1到l2s_distance行分配方式为{长-长-长 …},第l2s_distance+1到lsef_length行分配方式为{长-短-长-短 …}。第lsef_length+1行到下个垂直同步信号分配方式为{短-短-短 …}。

MIPI-Rx必须确保发送给ISP的长曝帧与短曝帧行数是一致的。

调整sensor短曝长度,有可能l2s_distance需要一起调整。

有些sensor可能会在送完短曝有效数据后带dummy行。 这会造成长曝与短曝的行数不一致。 可将l2s_distance设成0,lsef_length设成最大值0x1FFF,discard_padding_lines为1即收下两张带有效与dummy数据的长短曝,再用ISP crop有效位置即可。