3. Confirm Specifications¶

3.1. Confirm Main Processor Specifications¶

Supported upper limit of Combo PHY input frequency.

Supported Combo PHY lane configuration.

Supported linear/WDR interface modes.

Supported I2C bus number.

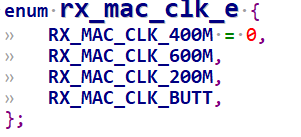

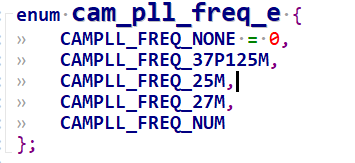

Supported output reference clock.

For example, cv181x supports the following:

3.2. Confirm Sensor Specifications¶

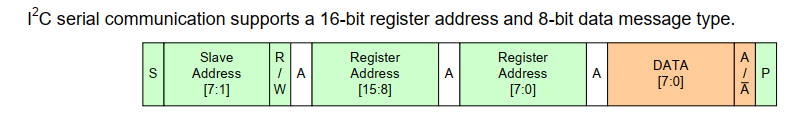

Confirm Sensor Control Interface (I2C/SPI).

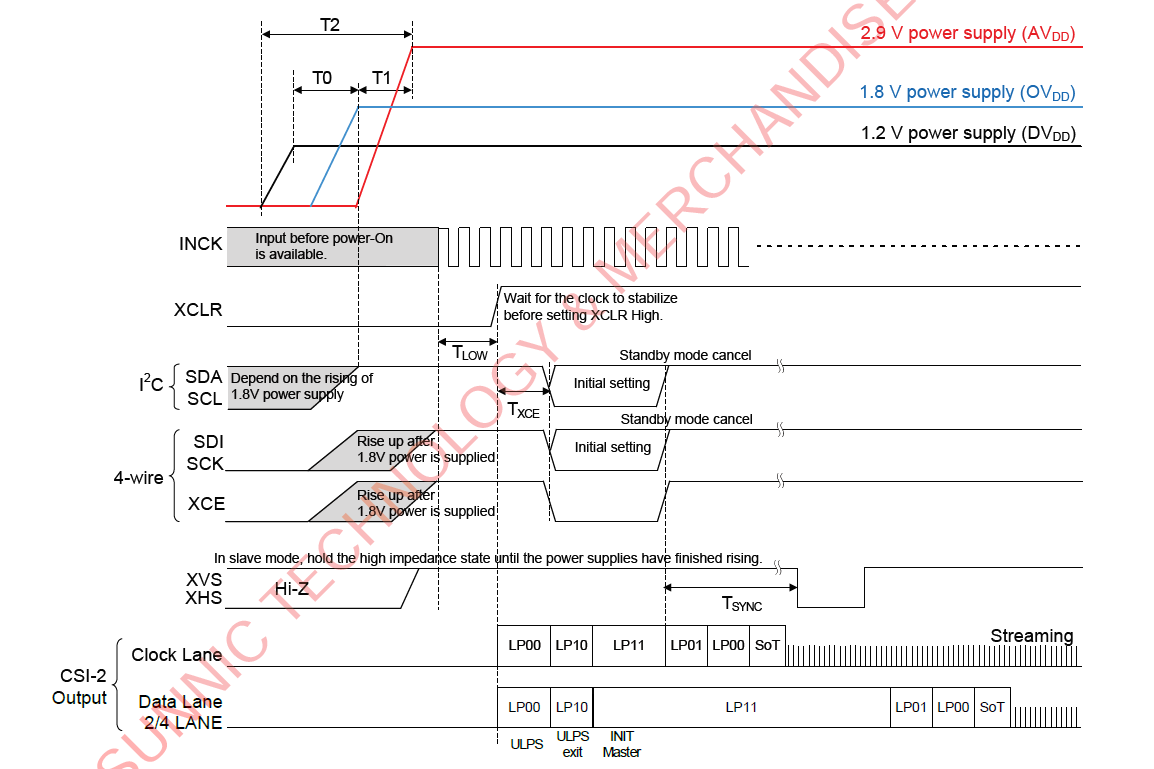

Confirm Sensor Power-on Sequence.

Confirm sensor input reference clock.

Confirm Bayer pattern and pixel code width.

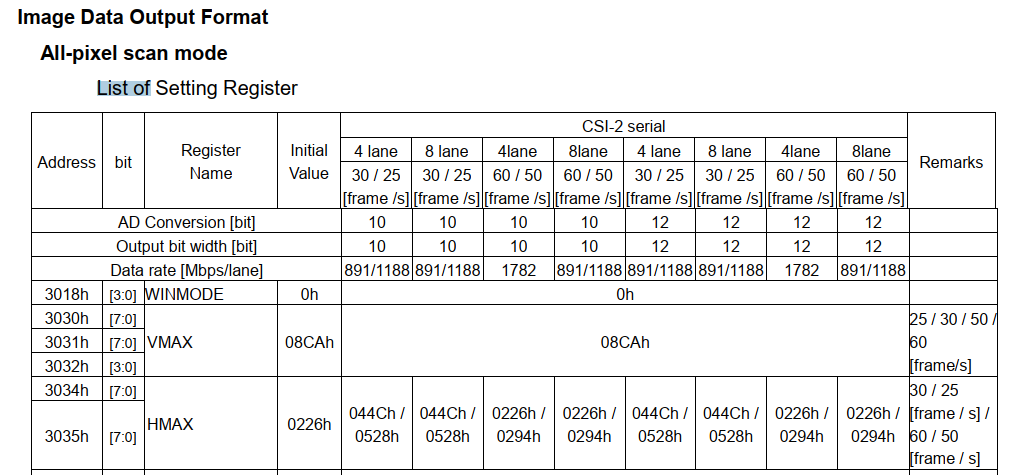

Confirm the image transfer interface mode and output frequency for linear/WDR mode.

Confirm how to set exposure time and gain for linear/WDR mode.

Confirm how to modify frame rate for linear/WDR mode.

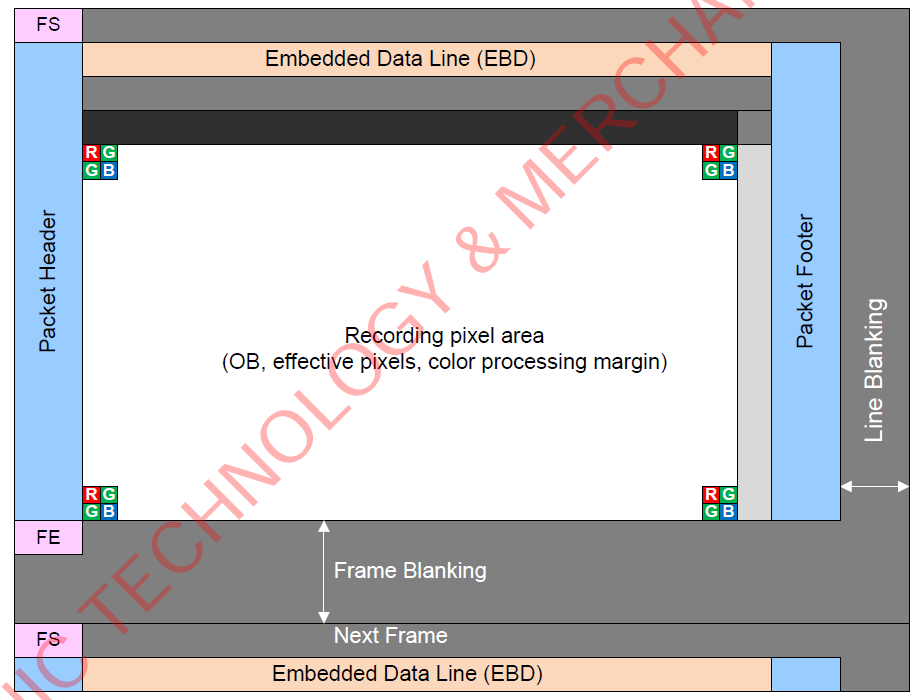

Confirm the sync code when the interface is subLVDS/HiSPi.

Request Sensor Initialize Settings from the sensor manufacturer.